## Broadband High-Efficiency Monolithic InGaP/GaAs HBT Power Amplifiers For 3G Handset Applications

H. Jäger<sup>1,2</sup>, A. Grebennikov<sup>1</sup>, E. Heaney<sup>1</sup> and R. Weigel<sup>2</sup>

<sup>1</sup> M/A-COM Eurotec Operations, Cork, Ireland

<sup>2</sup> University of Linz, Austria

**Abstract** - In this paper, an approach to high efficiency power amplifier performance over a wide frequency range is discussed. Results for a practical implementation of a multi-band and multi-mode handset power amplifier are shown. Measurements demonstrate feasibility of the concept for WCDMA, DCS1800 and PCS1900 high-efficient operation. A PAE of better than 38 % at 27 dBm output power and an ACLR of -37 dBc in WCDMA operation, as well as greater than 50 % PAE at 30 dBm output power in the DCS1800 and PCS1900 band are documented.

### I. INTRODUCTION

Third generation cellular phone systems like Wideband CDMA or CDMA2000 place high demands to their transmitter performance for high-efficiency operation should be provided with high linearity. Therefore, the main direction in the power amplifier (PA) design is to propose an adequate circuit configuration, which minimizes current consumption, cost and size and maximizes talk time, battery life and operation linearity. However, it is not easy to satisfy simultaneously such contradictory requirements as efficiency and linearity. For example, using a high efficiency performance InGaP/GaAs HBT device it is possible to achieve a saturated power-added efficiency (PAE) of about 50% for 31-dBm output power. But to satisfy the linearity requirements, it is necessary to reduce the output power down to 26 dBm to achieve a level of adjacent channel leakage ratio (ACLR) of -37 dBc [1]. With enhancement mode power PHEMT process, it is possible to provide 35 dBm output power with 55% PAE for GSM900 PA and 33 dBm with 40 % PAE for DCS1800 PA [2]. In addition, for cost and size reduction it is very advisable to realize a broadband operation without additional tuning, for example, to overlap simultaneously DCS1800 and W-CDMA or CDMA2000 bandwidths, i.e. to provide the broadband high-efficiency operation conditions with minimum gain flatness in a frequency range of 1.71-1.98 GHz.

In order to realize a high efficiency broadband operation with the current and voltage waveforms corresponding to the switched-mode operation conditions it is necessary to use a special broadband load network. For example, a

simple network consisting of a series resonant *LC* circuit tuned on the fundamental and a parallel inductance, which provides a constant load phase angle of 50° in 50% relative bandwidth [3]. For the first time, such a reactance compensation technique, employing single-resonant circuits, was applied to varactor-tuned Gunn oscillator and parametric amplifier [4]. Reactance compensation circuit technique can also be applied to microwave transistor amplifier design, because the input and output transistor impedances are generally simulated by series or shunt *LC* and transmission-line circuits. For compensating the reactive part and transforming the active part of the output transistor impedance to the conventional load impedance, the quarter-wavelength or half-wavelength transmission lines can also be effectively used. So, the transmission-line matching technique allows realizing for GaAs MESFET amplifier a frequency range of 3.7-4.2 GHz with a gain ripple in limits of  $\pm 0.1$  dB and return losses about 20 dB [5].

### II. ANALYSIS

#### A. Single Reactance Compensation with Lumped Elements

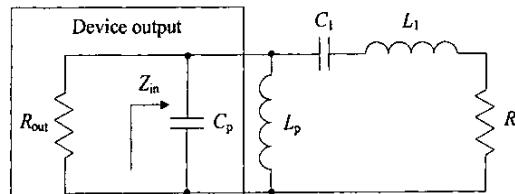

To describe reactance compensation circuit technique consider the simplified equivalent loading circuit with a series  $L_0C_0$  resonant circuit tuned on the fundamental and a shunt *LC* circuit providing a constant load phase angle relatively the device output terminals shown in Figure 1.

Fig. 1. Single reactance compensation circuit

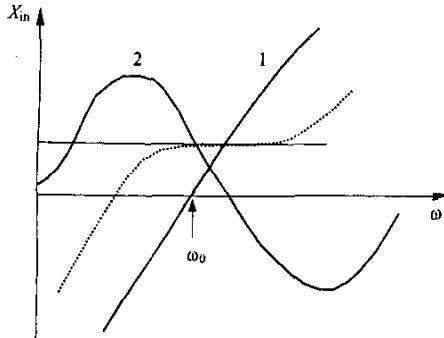

The reactances of the series and shunt resonant circuits vary with frequency, increasing in the case of series circuit and reducing in the case of loaded parallel circuit near the

resonant frequency  $\omega_0$ , as shown in Figure 2 by curve 1 and curve 2, respectively. And near the resonant frequency  $\omega_0$  of the series circuit with positive slope of its reactance the slope of shunt circuit reactance is negative, which reduces the overall reactance slope of the loading network (dotted line). By proper choice of the circuit elements a constant load angle can be provided over a very large frequency bandwidth.

Fig. 2. Reactance compensation principle

This technique can be easily applied to switched-mode power amplifiers with parallel circuit [6]. In this case, the optimum load resistance  $R$  and phase angle  $\Phi$  of the load network can be represented as a function of the circuit parameters as

$$R = 1.365 \frac{V_{cc}^2}{P_{out}} \quad (1)$$

$$\phi = \tan^{-1} \left( \frac{R}{\omega L} - \omega RC \right) = 34.244^\circ \quad (2)$$

where  $V_{cc}$  is the supply voltage and  $P_{out}$  is the output power.

The load network input admittance  $Y_{in} = 1/Z_{in}$  can be written by

$$Y_{in} = \left( j\omega C + \frac{1}{j\omega L} + \frac{1}{R + j\omega' L_0} \right) \quad (3)$$

where  $\omega' = \omega \left( 1 - \frac{\omega_0^2}{\omega^2} \right)$ ,  $\omega_0 = 1/\sqrt{L_0 C_0}$  is the resonant

frequency. The shunt capacitance  $C$  and inductance  $L$  required for optimum switched-mode operation are calculated as the functions of the load resistance  $R$ , respectively, from [6]

$$L = 0.732 \frac{R}{\omega} \quad (4)$$

$$C = \frac{0.685}{\omega R} \quad (5)$$

The parameters of the series  $L_0 C_0$  resonant circuit must be chosen so that to provide a constant phase angle of the

load network over a broadband frequency bandwidth. This bandwidth will be maximized if at resonance frequency  $\omega_0$

$$\frac{dB(\omega)}{d\omega} \Big|_{\omega=\omega_0} = 0 \quad (6)$$

where  $B(\omega) = \text{Im}(Y_{in}) = 1 - \omega^2 LC / \omega L$  is the load network susceptance. In this case, in order to simplify the calculation procedure the concept of the susceptance reactance compensation is used which is absolutely similar to the reactance compensation one. Then, an additional equation can be written by

$$C + \frac{1}{\omega^2 L} - \frac{2L_0}{R^2} = 0 \quad (8)$$

As a result, the series capacitance  $C_0$  and inductance  $L_0$  can be calculated by

$$L_0 = 1.026 \frac{R}{\omega} \quad (9)$$

$$C_0 = 1/\omega^2 L_0 \quad (10)$$

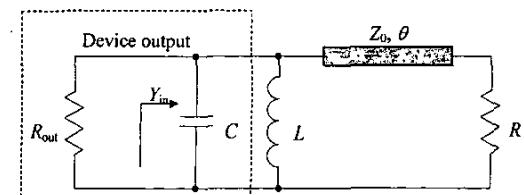

### B. Reactance compensation with transmission lines

Generally, the transmission lines are used as the elements of the matching circuits or a quarter-wavelength transformer to ensure the appropriate transformation of the real parts of the input or output transistor impedances into the real part of the load. Using a quarter-wavelength transformer the reactance compensation can be also realized with different topologies for shunt and series equivalent transistor circuits [5]. Let us consider the characteristics of the transmission line as an element of the reactance compensation circuit shown in Figure 3. For the parallel equivalent circuit, which represents the active device output, the overall load network reactance can be defined by

$$B(\omega) = \omega LC \left( 1 - \frac{\omega_0^2}{\omega^2} \right) + \frac{\tan \theta}{Z_0} \frac{R^2 - Z_0^2}{R^2 + Z_0^2 \tan^2 \theta} \quad (11)$$

where

$\theta = \frac{\pi f}{2 f_0} k$ ,  $f_0 = \omega_0/2\pi$  is the transmission line resonant

frequency,  $k = 1, 2, \dots, \infty$ ,  $Z_0$  is the transmission line characteristic impedance.

Fig. 3. Reactance compensation circuit with transmission line

Applying the condition (6) to equation (11) allows calculating the reactance compensation circuit parameters for

different electrical lengths of the transmission line in accordance with

$$2C + \frac{\pi}{2Z_0\omega_0} \frac{R^2 - Z_0^2}{\cos^2\theta} \frac{R^2 - Z_0^2 \tan^2\theta}{(R^2 + Z_0^2 \tan^2\theta)^2} = 0 \quad (12)$$

For a quarter-wave transmission line, when  $k = 1$  and  $\theta = \pi/2$ , the reactance compensation will be performed under the condition  $Z_0 < R$  and the value of the characteristic impedance  $Z_0$  can be defined from the quadratic equation

$$Z_0^2 + 4 \frac{QR}{\pi} Z_0 - R^2 = 0 \quad (13)$$

where  $Q = \omega CR_{out}$  and  $R_{out} = Z_0^2/R$ .

Consequently, the required value of the characteristic impedance  $Z_0$  is equal to

$$Z_0 = R \left( -\frac{2Q}{\pi} + \sqrt{\left( \frac{2Q}{\pi} \right)^2 + 1} \right) \quad (14)$$

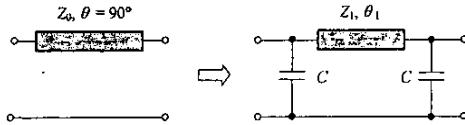

As it follows from equation (14), maximum value of the characteristic impedance  $Z_0$  is limited by the load resistance  $R$ , which is substantially smaller compared with 50 Ohm load that causes a problem in transmission line practical implementation. Moreover, the characteristic impedance becomes smaller still for low  $Q$ -values close to unity. In this case, it is advisable to apply single frequency equivalent replacement technique when a quarter-wave transmission line can be replaced by the symmetrical  $\pi$ -type low-pass transmission-line section with equal two shunt capacitances at a single frequency  $\omega_0$  as it is shown in Figure 4.

Fig. 4 Single frequency equivalent replacement technique

The  $ABCD$ -matrix for a quarter-wave transmission line can be written by

$$ABCD_{90^\circ} = \begin{bmatrix} 0 & jZ_0 \\ j\frac{1}{Z_0} & 0 \end{bmatrix} \quad (15)$$

whereas for  $\pi$ -type low-pass transmission-line section the  $ABCD$ -matrix can be given by

$$\begin{bmatrix} \cos\theta_1 - \omega CZ_1 \sin\theta_1 & jZ_1 \sin\theta_1 \\ j\omega CZ_1 \sin\theta_1 (2\cos\theta_1 - \omega CZ_1) & \cos\theta_1 - \omega CZ_1 \sin\theta_1 \end{bmatrix}. \quad (16)$$

Hence, equalizing  $A$  and  $B$  elements from each matrix gives

$$Z_1 = \frac{Z_0}{\sin\theta_1} \quad (17)$$

$$C = \frac{\cos\theta_1}{\omega Z_0} \quad (18)$$

As a result, the length of the transmission line can be reduced significantly with the increase of its characteristic impedance at the same time. Also, such a transformation is very important when the value of the device output capacitance exceeds the required optimum one for switched-mode operation. In this case, the excess capacitance can be used as a part or whole shunt capacitance in the  $\pi$ -type low-pass section and the optimum condition at least on the fundamental frequency will be completely satisfied.

### III. EXPERIMENTAL RESULTS

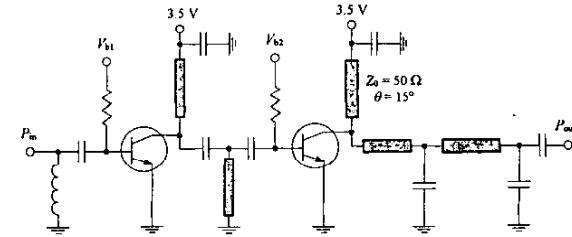

Utilizing the findings above, a two-stage power amplifier, depicted in Figure 5, targeted for WCDMA power class 2, was designed. The InGaP/GaAs HBT MMIC contains the RF devices, input match, interstage match and bias circuits on a die measuring less than 1 mm<sup>2</sup>. The emitter areas of the first and second stage are 540  $\mu\text{m}^2$  and 3600  $\mu\text{m}^2$ , corresponding to a median time to failure (MTTF) greater than  $8 \cdot 10^5$  hours at the desired power level. The MMIC, packaged in a 3 x 3 mm FQFP package was mounted on a FR4 PCB which contains the output matching circuit and microstrip transmission lines. The output matching circuit was built up according to the optimum values from a detailed simulation. Standard ceramic chip capacitors were used, and no more additional tuning was done.

Fig. 5. Schematic of two-stage broadband low-voltage InGaP/GaAs HBT power amplifier for handset application

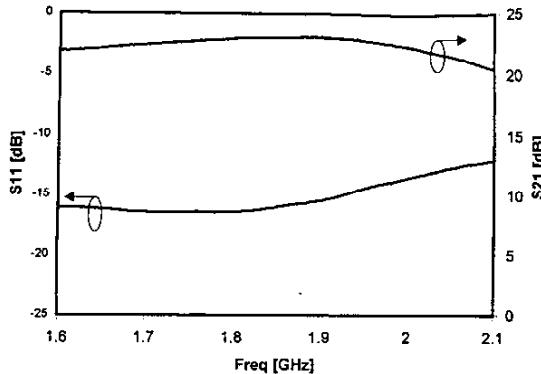

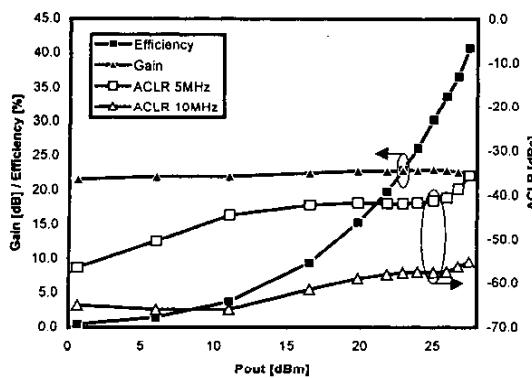

Figure 6 shows that the gain is 22.5 dB  $\pm 0.5$  dB and the input return loss is greater than 13 dB from 1.6 GHz to more than 2 GHz, confirming the wideband operation of the amplifier. Measurements in the WCDMA band, centered at 1.95 GHz, yield a PAE of 38.3 %, 22.6 dB gain, ACLR of -37 dBc in 5 MHz offset and -56 dBc in 10 MHz offset at 27 dBm output power. The channel measurement bandwidth was set to 3.84 MHz. In Figure 7, these parameters are displayed vs. output power. Of the upper and lower ACLR, only the worst cases are contained.

Fig. 6. Measured gain and input return loss at an input power level of 0 dBm

Fig. 7. Gain, efficiency and ACLR with a WCDMA signal at 1.95 GHz

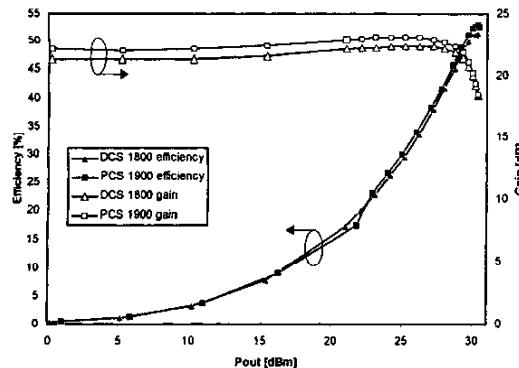

Fig. 8. PAE and Gain in the DCS and PCS band

The broadband capability of the PA was verified with regard to the DCS1800 and PCS1900 frequency bands. Without any tuning of the output matching circuit, a saturated RF output power greater than 30 dBm and PAE greater than 50 % were obtained. These single-tone measurements, depicted in Figure 8, were performed at the respective band centers, 1.75 GHz and 1.88 GHz.

Results obtained from four more sample PCBs are practically identical, demonstrating excellent repeatability as well as low component value and placement sensitivity. During all testing, the circuits exhibited stable and reliable performance, even at overrated power and voltage experiments.

### III. CONCLUSIONS

The concept of reactance compensation in combination with the switched-mode operating condition to obtain high efficiency over a wide band was discussed. The theoretical results were applied to a third-generation handset PA design. In WCDMA compliant operation, PAE was better than 38 % at 27 dBm output power and an ACLR of -37 dBc. Without any tuning, the same PCBs achieved greater than 50 % PAE and 30 dBm output power in the DCS1800 and PCS1900 band. These measurement results confirm the viability of the approach for multi-band and multi-mode operation.

### REFERENCES

1. T. B. Nishimura, M. Tanomura, K. Azuma, K. Nakai, Y. Hasegawa, and H. Shimawaki, "A 50% efficiency In-GaP/GaAs HBT power amplifier module for 1.95 GHz wide-band CDMA handsets" in *2001 IEEE RFIC Symp. Dig.*, pp. 31-34.

2. S. Zhang, J. Cao, and R. Mcmorrow, "E-PHEMT, single supply, high efficient power amplifiers for GSM and DCS applications" in *2001 IEEE MTT-S Int. Microwave Symp. Dig.*, pp. 927-930.

3. J. K. A. Everard, and A. J. King, "Broadband power efficient class E amplifiers with a non-linear CAD model of the active MOS device," *J. IERE*, Vol. 57, pp. 52-58, March 1987.

4. C. S. Aitchison, and R. V. Gelfthorpe, "A circuit technique for broadbanding the electronic tuning range of gunn oscillators," *IEEE J. Solid-State Circuits*, Vol. SC-12, pp. 21-28, Feb. 1977.

5. E. Camargo, and D. Consoni, "Reactance compensation matches FET circuits," *Microwaves*, Vol. 24, pp. 93-95, June 1985.

6. A. V. Grebenikov, and H. Jaeger, "Class E with parallel circuit - a new challenge for high-efficiency RF and microwave power amplifiers", in *2002 IEEE MTT-S International Microwave Symposium Digest*, section 14.